## **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

# Novel Design Approach and Architectures for Sinusoid Output Direct Digital Frequency Synthesis

# Conception et Architectures Nouvelles pour Synthétiseurs Numériques de Fréquences

A Thesis Submitted

to the Department of Electrical and Computer Engineering

of the Royal Military College of Canada

by

Joseph Mathieu Pierre Langlois, CD, rmc, B.Eng., M.Eng., P.Eng. Lieutenant-Commander

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

September 2002

©This thesis may be used within the Department of National Defence but copyright for open publication remains the property of the author.

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Oltawa ON K1A 0N4 Canada

Your Re Votes référence

Our Ste Notre mildrence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-71892-1

# Acknowledgements remerciements

Let us state the obvious: this thesis could not have been completed without the assistance and support from several people. I would therefore like to express my sincere gratitude to all of them.

Dr. Dhamin Al-Khalili, for his constant involvement and interest in this research, even during his sabbatical leave, and for his outstanding ability at turning apparent dead ends into fruitful ideas.

Dr. Valek Szwarc, for suggesting research on Direct Digital Frequency Synthesis.

Dr. Gilles Labonté pour son introduction succincte aux algorithmes génétiques, qui ont permis de débloquer cette recherche. Dr. Robert Gervais, pour avoir révisé une partie des dérivations mathématiques. Dr. Lucien Haddad et Dr. Philippe Baille, pour les discussions sur de nouvelles idées. Dr. Robert Benesch et Dr. Jean Fugère, pour leur support constant depuis cinq ans.

Jean-Luc Derome, pour l'aide avec les outils Cadence<sup>TM</sup>. Jennifer Mullan, pour la multitude d'articles obtenus d'obscures conférences. Mariusz Jarosz, for his help during hardware testing.

The Canadian Microelectronics Corporation, for the availability of design tools and for grants of fabrication area.

Mes parents, Mariette Drouin et Rodolphe Langlois.

Mon épouse et meilleure amie, Caroline Dion, pour avoir accepté que j'accorde autant de mon temps et de mon énergie à ce travail.

Cette dissertation est dédiée à mes enfants, Évelyne et Étienne, et à mon épouse Caroline.

# **Abstract**

Langlois, Joseph Mathieu Pierre, Royal Military College of Canada, May 2002, Novel Design Approach and Architectures for Sinusoid Output Direct Digital Frequency Synthesis

Supervisor: Dr. Dhamin Al-Khalili

Direct Digital Frequency Synthesis (DDFS) makes it possible to generate single phase or quadrature sinusoids over bandwidths measured in hundreds of megahertz, with sub-hertz frequency resolution, unparalleled frequency hopping rates, and phase continuity on hopping. These characteristics make DDF Synthesizers ideal in a wide array of applications, including spread-spectrum communications, radar, instrumentation and broadcasting. Design challenges include maintaining high spectral purity, high clock rates and low power consumption.

This thesis presents a novel approach to the design of sinusoid output DDF Synthesizers with Phase-to-Sine Amplitude Converters based on linear interpolation. For such synthesizers, the first quadrant of the sine function is approximated with piecewise-continuous linear segments. Simple control circuitry reconstructs a full sine wave by symmetry.

Basic principles of DDFS are presented, and a comprehensive review of existing work is made. A spectral analysis of the linear interpolation of the sine function is given, from which a design procedure is derived for the number of segments required and the value of system parameters to achieve a desired spectral purity. New hardware-optimized single phase and quadrature DDFS architectures are presented, and their validity is supported by several designs implemented with three different technologies. The new design approach and architectures are compared with existing work and are shown to produce designs with significantly reduced complexity and power consumption for equal performance.

# résumé

Langlois, Joseph Mathieu Pierre, Collège militaire royal du Canada, juillet 2002, Conception et Architectures Nouvelles pour Synthétiseurs Numériques de Fréquences

Directeur de thèse: Dr. Dhamin Al-Khalili

Les synthétiseurs numériques de fréquences (SNF) génèrent des signaux sinusoïdaux en phase unique ou en quadrature sur des largeurs de bandes de plusieurs centaines de mégahertz, avec une résolution inférieure à un hertz, des taux de sauts en fréquences inégalés, en maintenant une continuité de phase lors d'un saut. Ces caractéristiques font des SNF les synthétiseurs de choix pour une vaste gamme d'applications, incluant les communications à dispersion de spectre, les systèmes radars, les instruments de mesure, et le domaine de la radiodiffusion. Cependant, il est souvent difficile de concevoir un SNF atteignant une haute pureté spectrale, une fréquence d'horloge élevée et une faible consommation de puissance.

Cette thèse présente une approche originale pour la conception de SNF à sortie sinusoïdale avec convertisseurs de phase à amplitude employant l'interpolation linéaire. Dans un tel cas, on fait l'approximation du premier quadrant de la fonction sinus par des segments de droite, et un circuit de contrôle permet de reconstruire une onde sinusoïdale complète par symétrie.

Les principes de base des SNF sont présentés, et une revue détaillée des travaux existants est faite. Une analyse spectrale de l'interpolation linéaire de la fonction sinus est donnée, menant à une relation entre la pureté spectrale désirée, le nombre de segments nécessaires, et la valeur des paramètres du système. De nouvelles architectures de SNF optimisées pour réalisation matérielle sont présentées, et leur validité est supportée par plusieurs exemples appliqués à trois différentes technologies. La nouvelle approche de conception et les nouvelles architectures sont comparées aux travaux existants, démontrant que la complexité et la consommation de puissance des synthétiseurs résultants est significativement moindre pour des performances égales.

# **Table of Contents**

| List of Figures | xii                                                     |

|-----------------|---------------------------------------------------------|

| List of Tables  | xv                                                      |

| Acronyms        | xvi                                                     |

| Chapter 1       | Introduction 1                                          |

| 1.1 Overvi      | iew 1                                                   |

| 1.2 Motiva      | ation                                                   |

| 1.3 Resear      | rch Objectives4                                         |

| 1.4 Synop       | sis4                                                    |

| Chapter 2       | Principles of Direct Digital Frequency Synthesis        |

| 2.1 Direct      | Digital Frequency Synthesizer Architecture              |

| 2.1.1 G         | General Description                                     |

| 2.1.2 T         | uned Frequency and Effect of the Frequency Control Word |

| 2.1.3 F         | requency Resolution 8                                   |

| 2.1.4 T         | uning Bandwidth9                                        |

| 2.1.5 T         | Cuning Latency                                          |

| 2.1.6 P         | hase Continuity upon Tuning                             |

| 2.1.7 F         | requency and Phase Modulation                           |

| 2.1.8 C         | Other Output Types                                      |

| 2.2 Phase       | to Sinusoid Amplitude Converter Complexity Reduction    |

| 2.2.1   | Phase Angle Truncation                                         | 12 |

|---------|----------------------------------------------------------------|----|

| 2.2.2   | Exploiting Quadrant Symmetry                                   | 13 |

| 2.2.3   | Quadrature Sinusoid Outputs Architecture                       | 16 |

| 2.3 Out | tput Noise                                                     | 17 |

| 2.3.1   | Noise Due to Amplitude Error                                   | 17 |

| 2.3.2   | Noise Due to Phase Truncation                                  | 20 |

| 2.3.3   | Phase Noise                                                    | 20 |

| 2.3.4   | Noise Reduction Techniques                                     | 21 |

| 2.4 Clo | ock Output DDFS                                                | 22 |

| 2.5 Sys | stem Performance Parameters and DDFS Complexity Metrics        | 23 |

| 2.5.1   | Performance Parameters                                         | 23 |

| 2.5.2   | Hardware Implementation Complexity Metrics                     | 25 |

| Chapte  | T 3 State of the Art in Phase to Sinusoid Amplitude Conversion | 27 |

| 3.1 An  | gular Decomposition                                            | 27 |

| 3.1.1   | Tierney et al.: Sum of Angles and Multiplication               | 27 |

| 3.1.2   | Hutchinson: Sum of Two Angles, Approximations and Addition     | 30 |

| 3.1.3   | Sunderland et al.: Sum of Three Angles                         | 30 |

| 3.1.4   | Nicholas et al.: Exhaustive Search                             | 32 |

| 3.1.5   | Goldberg: Auxiliary Functions                                  | 33 |

| 3.2 Sin | ne Amplitude Compression                                       | 33 |

| 3.2.1   | Nicholas et al.: Sine-Phase Difference Algorithm               | 35 |

| 3.2.2   | Yamagishi et al.: Double Trigonometric Approximation           | 35 |

| 3.2.3 | Sodagar and Lahiji: Parabolic Approximation                                       | 37        |

|-------|-----------------------------------------------------------------------------------|-----------|

| 3.2.4 | Comparison                                                                        | 38        |

| 3.3   | Angle Rotation Based Methods                                                      | 40        |

| 3.4   | Polynomial Approximations                                                         | 41        |

| 3.4.1 | Freeman's Architecture                                                            | 42        |

| 3.4.2 | Bellaouar et al.: 1st Degree Taylor Series                                        | 43        |

| 3.4.3 | Liu et al.: Linear Segments of Unequal Lengths                                    | 45        |

| 3.4.4 | Curticăpean et al.: Angular Decomposition Revisited                               | 46        |

| 3.4.5 | Weaver and Kerr: 2 <sup>nd</sup> degree Taylor Expansion                          | 47        |

| 3.4.6 | Fanucci et al.: Quadratic Approximation                                           | 47        |

| 3.4.7 | De Caro et al.: Optimized Polynomials, 2 <sup>nd</sup> and 3 <sup>rd</sup> Degree | 48        |

| 3.4.8 | Sodagar and Lahiji: Simplified 4th Degree Polynomial                              | 49        |

| 3.4.9 | Palomäki and Niitylahti: High Degree Chebyshev Polynomials and Taylo 50           | or Series |

| 3.5   | PSAC-DAC Combinations                                                             | 51        |

| Chapt | ter 4 New Amplitude Compression Technique                                         | 53        |

| 4.1   | Review of Amplitude Compression                                                   | 53        |

| 4.2   | New Approximation and Architecture                                                | 54        |

| 4.2.1 | Linear Interpolation Scheme                                                       | 54        |

| 4.2.2 | 2 Design Example                                                                  | 56        |

| 4.2.3 | New Architecture                                                                  | 57        |

| 4.3   | Comparison of the New and Existing Techniques                                     | 58        |

|   | 4.4  | ROM-less Performance                                            | 60 |

|---|------|-----------------------------------------------------------------|----|

| C | Chap | ter 5 Analysis and Design of DDFS Based on Linear Interpolation | 61 |

|   | 5.1  | General System Architecture                                     | 61 |

|   | 5.2  | Output Spectral Analysis                                        | 63 |

|   | 5.3  | Upper Bound on SFDR given the Number of Linear Segments Used    | 67 |

|   | 5.4  | Linear Interpolation Coefficients Selection                     | 73 |

|   | 5.4. | 1 Selection Criteria for h(n), n = 3, 5, 7,, 4s - 3             | 73 |

|   | 5.4. | 2 Acceptable Range of Values for g(1) Given a Desired SFDR      | 77 |

|   | 5.4. | 3 Selection Criteria for g(n), n = 1, 3, 5, 7,, 2s - 1          | 78 |

|   | 5.5  | Design Procedure                                                | 79 |

|   | Chap | oter 6 New DDFS Architectures Based on Linear Interpolation     | 82 |

|   | 6.1  | New Architectures                                               | 82 |

|   | 6.1. | l General Description                                           | 82 |

|   | 6.1. | 2 Addend Alignment                                              | 85 |

|   | 6.1. | 3 Architecture Examples, Single Phase Output                    | 88 |

|   | 6.1. | 4 Quadrature Outputs Architecture                               | 90 |

|   | 6.2  | High Level PSAC Complexity Metrics                              | 93 |

|   | 6.2. | 1 System Coefficients and Parameters                            | 94 |

|   | 6.2. | 2 Complexity Metrics                                            | 94 |

|   | 6.2  | Number of ROM Bits                                              | 95 |

|   | 6.2  | 4 Number of 2:1 Multiplexers                                    | 95 |

|   | 6.2  | .5 Number of Full Adders                                        | 96 |

| 6.2.6   | Total Cost                                                               | 96    |

|---------|--------------------------------------------------------------------------|-------|

| 6.3 Des | ign Process and Design Examples                                          | 97    |

| 6.3.1   | Design Space Exploration and Selection of Coefficient and Parameter Sets | 97    |

| 6.3.2   | Candidate Slopes                                                         | 97    |

| 6.3.3   | Establishing a List of Groups of Acceptable Slopes                       | 99    |

| 6.3.4   | Exhaustive Search on M, L, C and D and Selection                         | . 102 |

| 6.3.5   | Output Data and Spectral Plots                                           | . 104 |

| 6.4 HD  | L System Description                                                     | . 112 |

| 6.4.1   | Automated VHDL Code Generation                                           | . 112 |

| 6.4.2   | Module Compiler Language™ Description                                    | . 113 |

| 6.5 Imp | lementation Data and Results                                             | . 114 |

| 6.5.1   | Implementation in Xilinx® FPGA                                           | . 114 |

| 6.5.2   | Implementation Details for 0.18 μm and 0.35 μm CMOS                      | . 115 |

| 6.5.3   | 0.18 µm Implementation Results                                           | . 115 |

| 6.5.4   | 0.35 µm Implementation Results                                           | 118   |

| 6.6 Fab | ricated Designs                                                          | 121   |

| 6.6.1   | 60 dBc Single Phase Design Description                                   | 121   |

| 6.6.2   | Test Strategy and Procedure                                              | 122   |

| 6.6.3   | Test Results                                                             | 123   |

| 6.6.4   | 84 dBc Design                                                            | 129   |

| Chapter | 7 Interpretation and Discussion.                                         | 130   |

| 7.1 Cor | mparison with State of the Art                                           | . 130 |

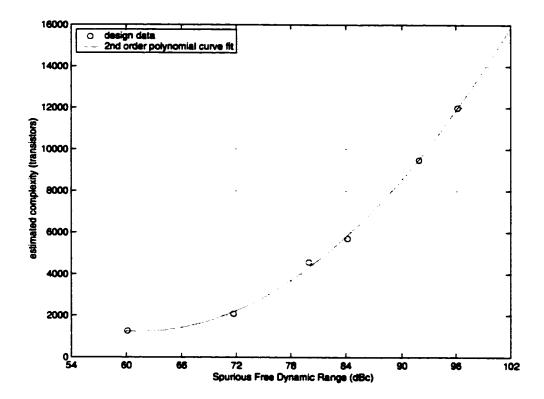

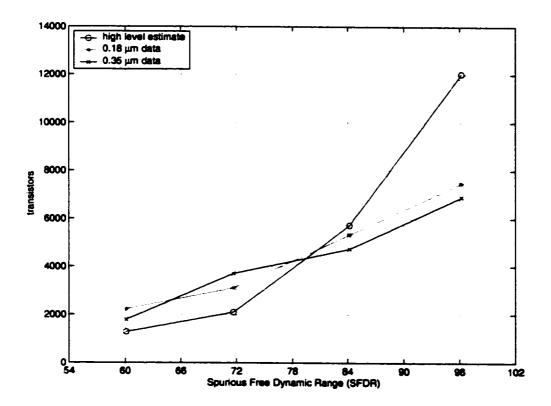

| 7.2     | Con           | nplexity Increase with SFDR Performance       | 133 |

|---------|---------------|-----------------------------------------------|-----|

| 7.      | 2.1           | Quadratic Relationship                        | 133 |

| 7.      | 2.2           | High Level Metrics versus Implementation Data | 134 |

| 7.      | 2.3           | 0.35 μm vs 0.18 μm Data                       | 135 |

| Cha     | pter          | 8 Conclusion                                  | 136 |

| 8.1     | Sum           | nmary of the Contribution                     | 136 |

| 8.2     | Con           | apletion of Research Objectives               | 136 |

| 8.3     | Rec           | ommendations for Future Work                  | 137 |

| Referen | nc <b>e</b> s |                                               | 140 |

| Bibliog | raphy.        |                                               | 148 |

| Vita    | Vita          |                                               | 151 |

# **List of Figures**

| Figure 2-1 - Single-phase sinusoid output DDFS architecture                         |

|-------------------------------------------------------------------------------------|

| Figure 2-2 - Varying the output frequency by skipping samples                       |

| Figure 2-3 - Quarter-wave symmetry (from [60])                                      |

| Figure 2-4 - Quadrature DDFS Architecture (from [90])                               |

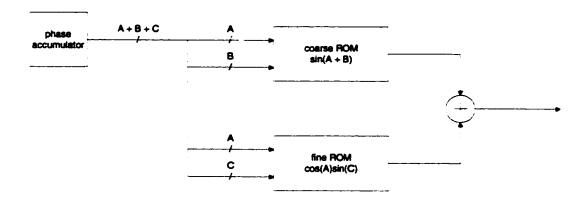

| Figure 3-1 - Sunderland approach                                                    |

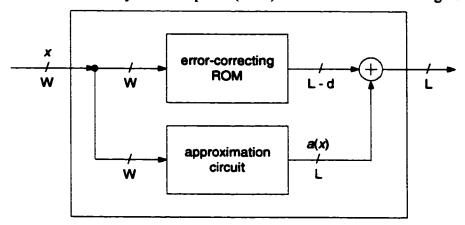

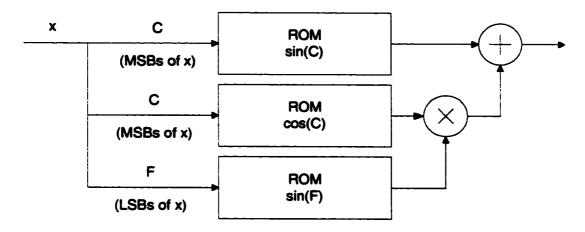

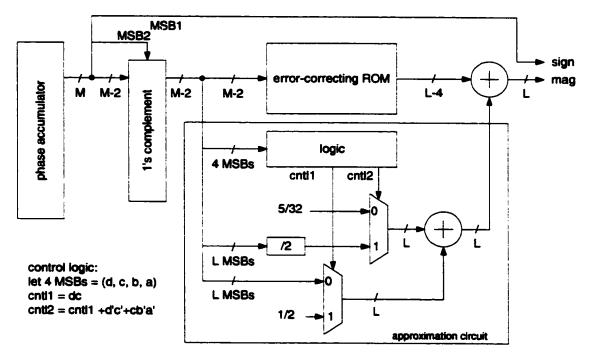

| Figure 3-2 - PSAC architecture based on amplitude compression                       |

| Figure 3-3 - Nicholas et al. approach - sine-phase difference algorithm             |

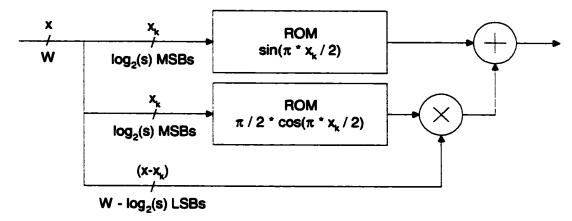

| Figure 3-4 - Yamagishi approach - double trigonometric approximation                |

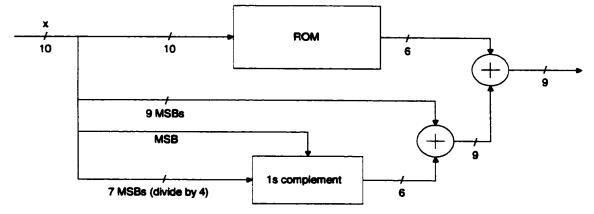

| Figure 3-5 - Sodagar and Lahiji approach - parabolic approximation                  |

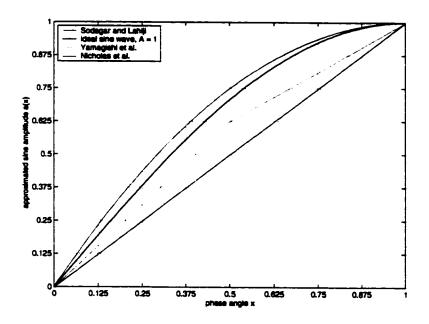

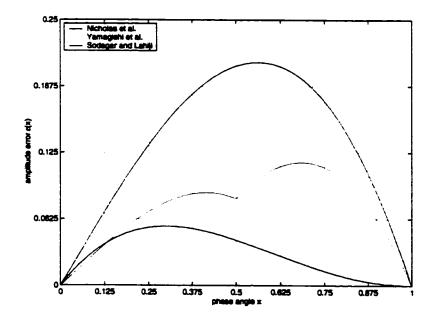

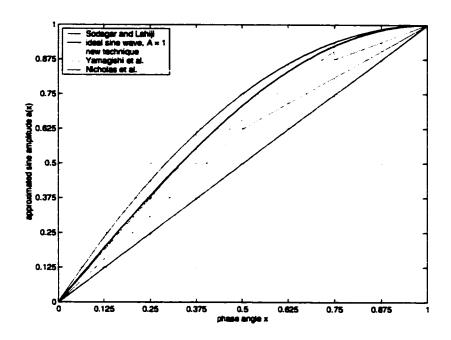

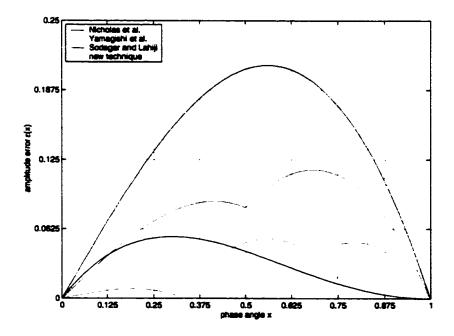

| Figure 3-6 - Sine function compression comparison – approximated curves             |

| Figure 3-7 - Sine function compression comparison - residual error                  |

| Figure 3-8 - Bellaouar et al.'s architecture (simplified)                           |

| Figure 3-9 - Curticăpean et al.'s architecture (simplified)                         |

| Figure 4-1 - New Amplitude Compression DDFS Architecture                            |

| Figure 4-2 - Comparison of new and existing architectures – approximating functions |

| Figure 4-3 - Comparison of new and existing architectures - residual error          |

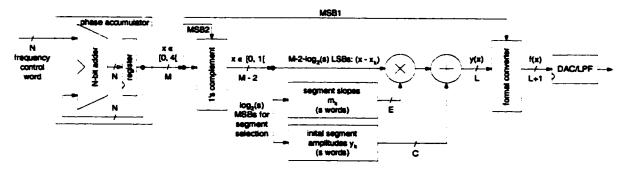

| Figure 5-1 - General architecture of single-phase DDFS using linear interpolation   |

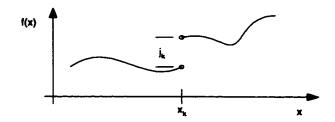

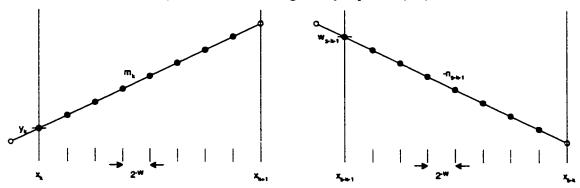

| Figure 5-2 - Jump in f at a discontinuity                                           |

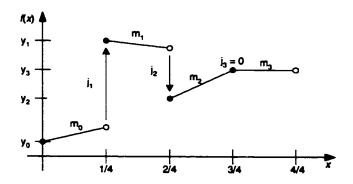

| Figure 5-3 - First quadrant of f defined by four linear segments                    |

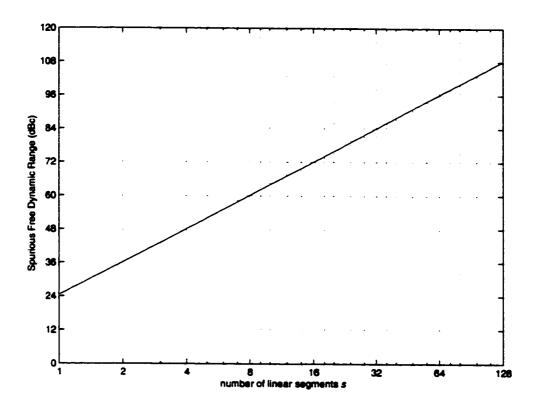

| Figure 5-4 - Upper bound on SFDR as a function of the number of linear segments used 73             |

|-----------------------------------------------------------------------------------------------------|

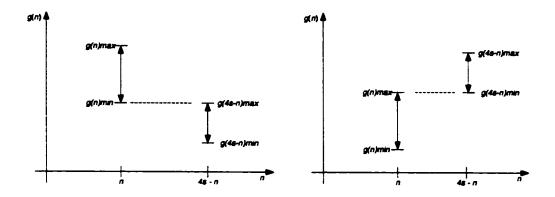

| Figure 5-5 - Two limit conditions for acceptable intervals for $g(n)$ , with $g(n) = g(4s - n)$     |

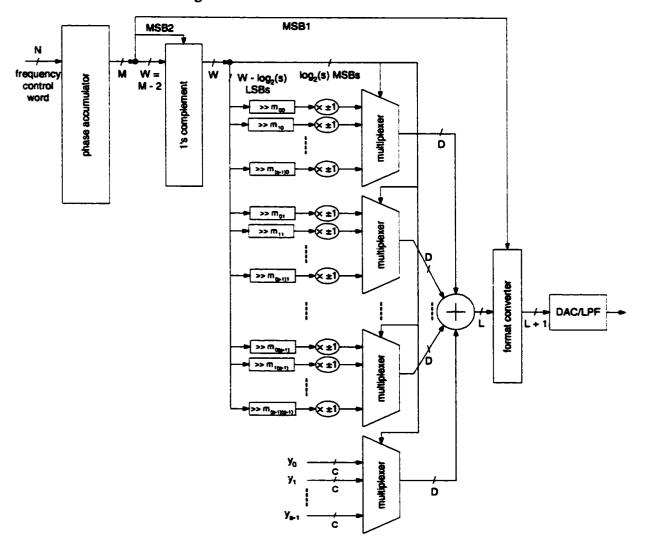

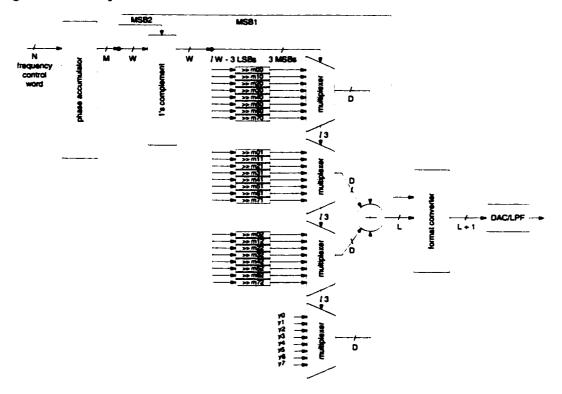

| Figure 6-1 Novel single-phase multiplier-less DDFS architecture, general format                     |

| Figure 6-2 - Decomposition of the phase angle word                                                  |

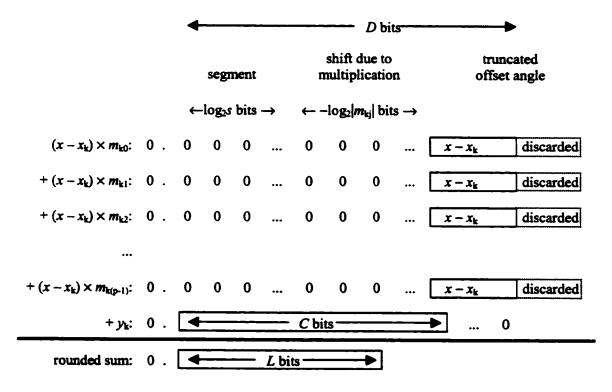

| Figure 6-3 - Addend alignment, general case                                                         |

| Figure 6-4 - Addend alignment, example 1                                                            |

| Figure 6-5 - Addend alignment, example 2                                                            |

| Figure 6-6 - Addend alignment, pre-addition optimization                                            |

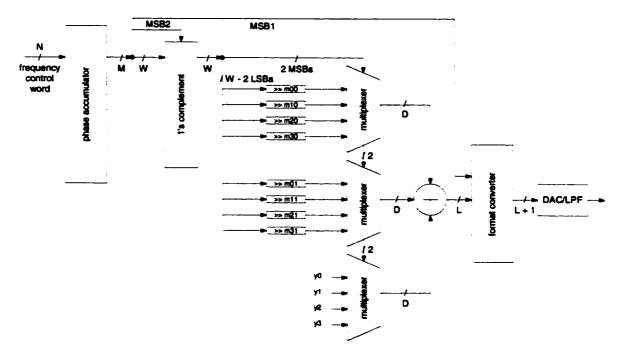

| Figure 6-7 - Novel multiplier-less DDFS architecture, four segments, slopes with two digits 89      |

| Figure 6-8 - Novel multiplier-less DDFS architecture, eight segments, slopes with two digits 89     |

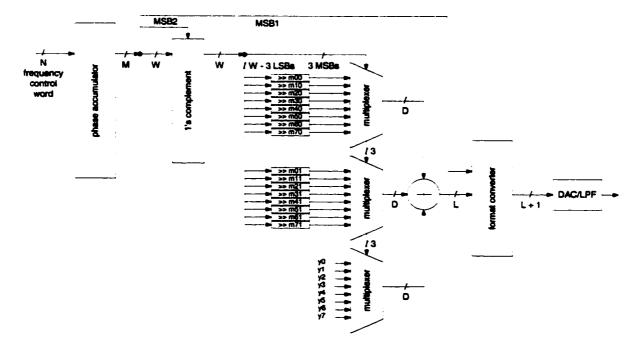

| Figure 6-9 - Novel multiplier-less DDFS architecture, eight segments, slopes with three digits . 90 |

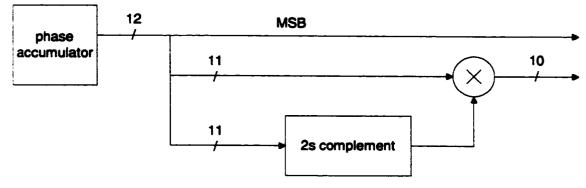

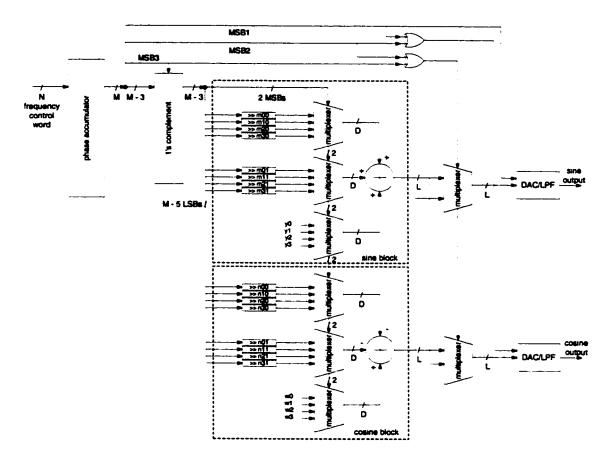

| Figure 6-10 - Coefficient conversion for quadrature DDFS                                            |

| Figure 6-11 - Novel multiplier-less QDDFS architecture, eight segments, slopes with two digits 93   |

| Figure 6-12 - Estimated PSAC complexity versus SFDR                                                 |

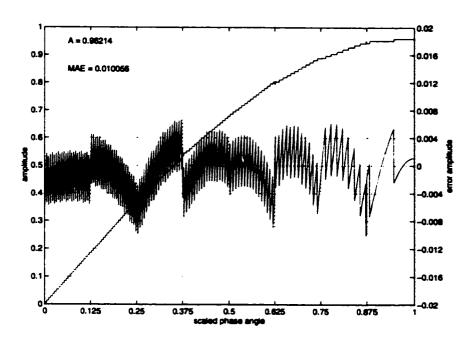

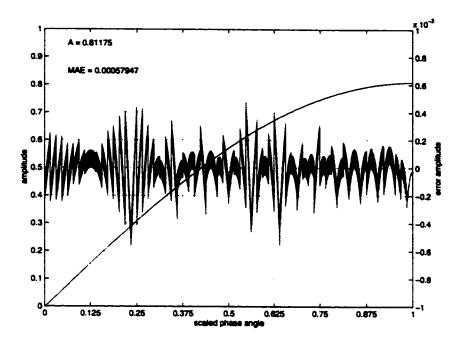

| Figure 6-13 - Output data and error, 8 segments, 60.1 dBc SFDR design                               |

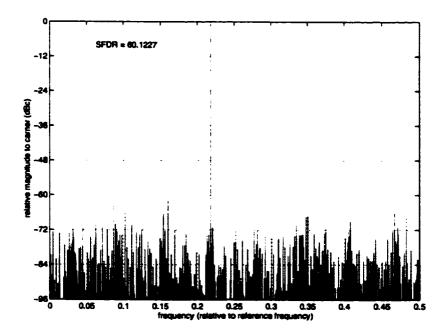

| Figure 6-14 - Typical spectral plot, 8 segments, 60.1 dBc SFDR design                               |

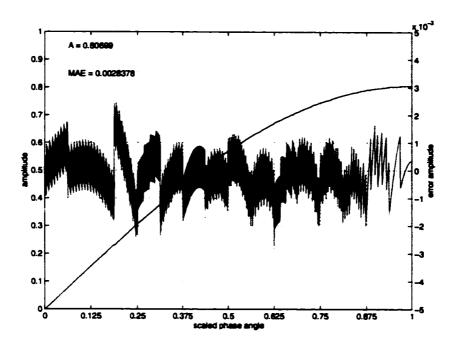

| Figure 6-15 - Output data and error, 16 segments, 71.7 dBc SFDR design                              |

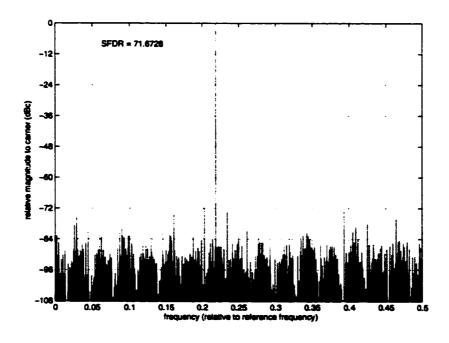

| Figure 6-16 - Typical spectral plot, 16 segments, 71.7 dBc SFDR design                              |

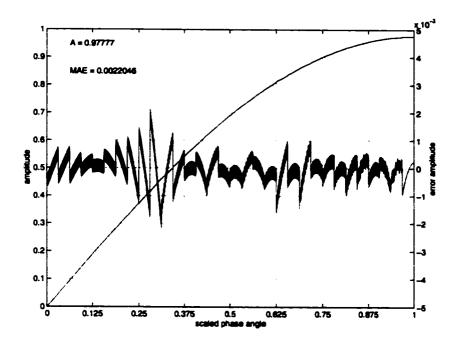

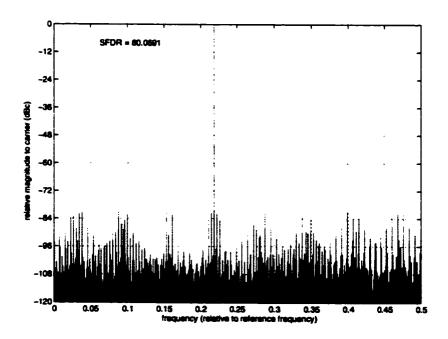

| Figure 6-17 - Output data and error, 32 segments, 80.0 dBc SFDR design                              |

| Figure 6-18 - Typical spectral plot, 32 segments, 80.0 dBc SFDR design                              |

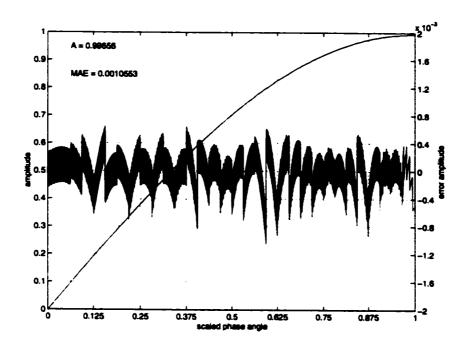

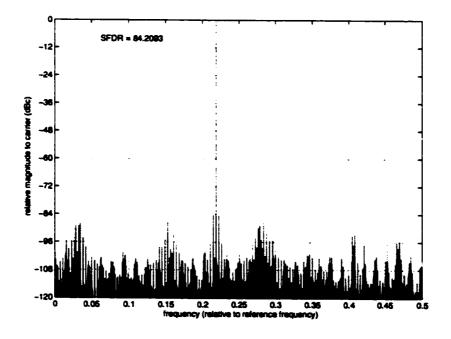

| Figure 6-19 - Output data and error, 32 segments, 84.2 dBc SFDR design                              |

| Figure 6-20 - Typical spectral plot, 32 segments, 84.2 dBc SFDR design                              |

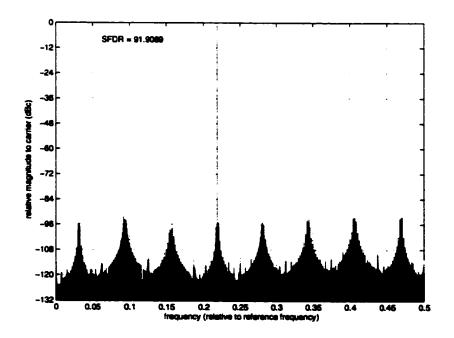

| Figure 6-21 - Output data and error, 64 segments, 91.9 dBc SFDR design | 110 |

|------------------------------------------------------------------------|-----|

| Figure 6-22 - Typical spectral plot, 64 segments, 91.9 dBc SFDR design | 110 |

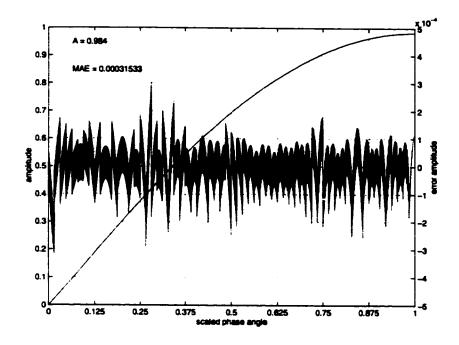

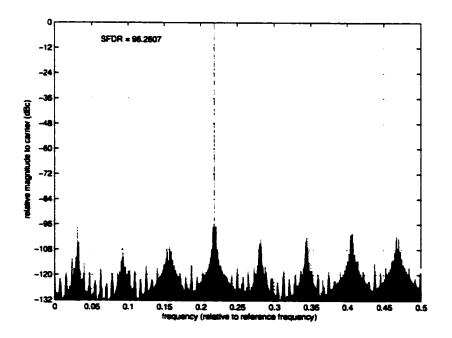

| Figure 6-23 - Output data and error, 64 segments, 96.2 dBc SFDR design | 111 |

| Figure 6-24 - Typical spectral plot, 64 segments, 96.2 dBc SFDR design | 111 |

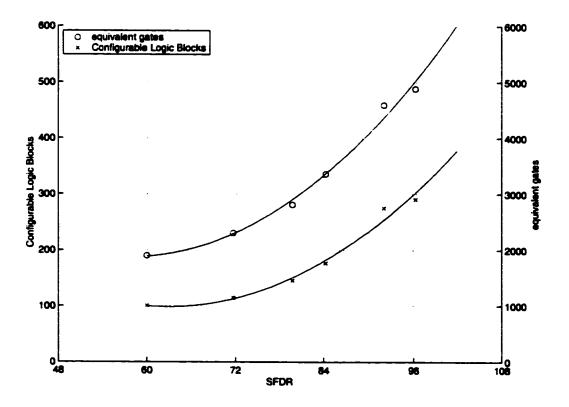

| Figure 6-25 - FPGA implementation statistics                           | 114 |

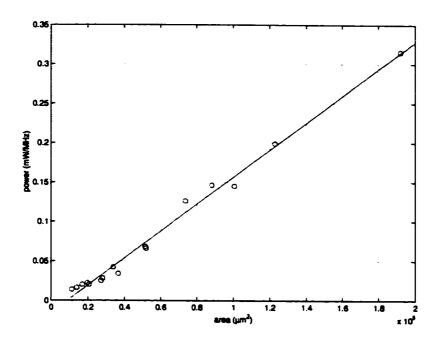

| Figure 6-26 - Power vs area, 0.18 µm CMOS worst case library           | 117 |

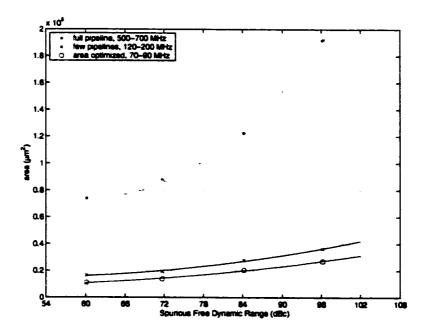

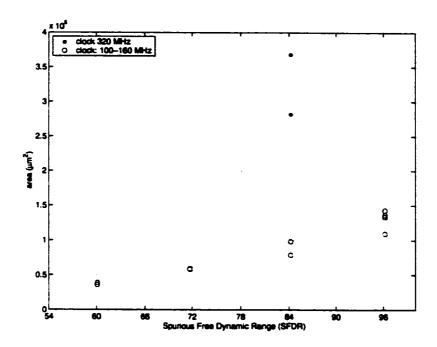

| Figure 6-27 - Area vs SFDR, 0.18 µm CMOS worst case library            | 117 |

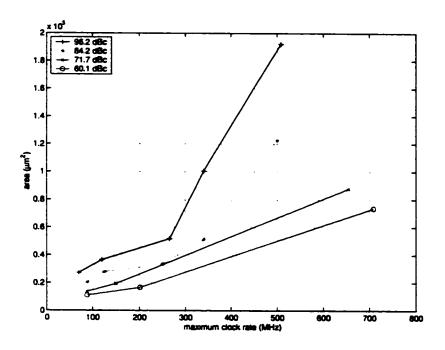

| Figure 6-28 - Area vs clock rate, 0.18 µm CMOS worst case library      | 118 |

| Figure 6-29 - Area vs SFDR, 0.35 μm CMOS typical case library          | 120 |

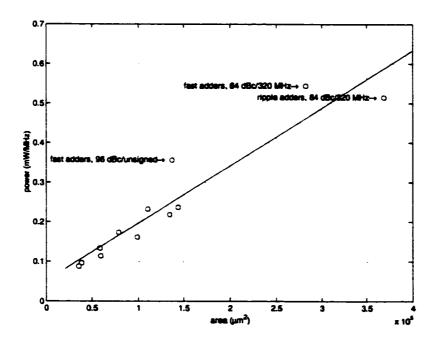

| Figure 6-30 - Power vs area, 0.35 μm CMOS typical case library         | 120 |

| Figure 6-31 - Die picture, 60 dBc single phase DDFS in 0.18 μm CMOS    | 121 |

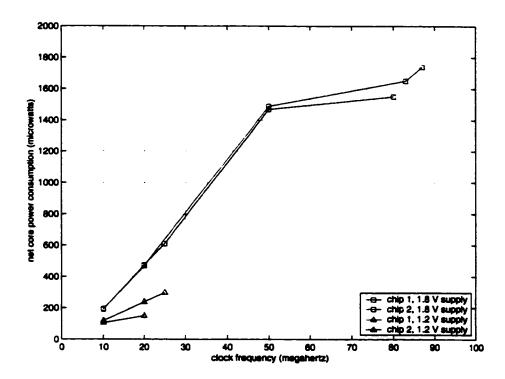

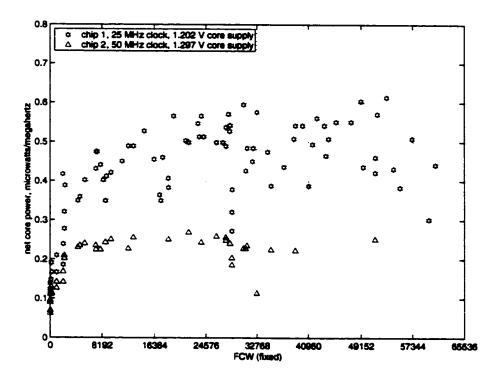

| Figure 6-32 - Net core power consumption                               | 126 |

| Figure 6-33 - Net core power consumption versus FCW input (fixed FCW)  | 127 |

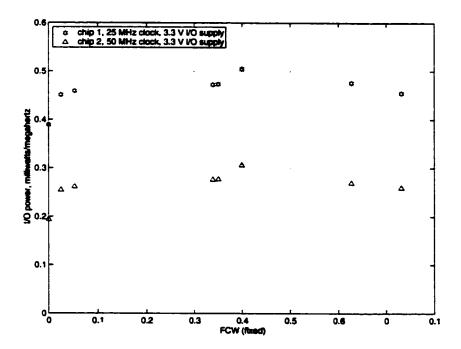

| Figure 6-34 - I/O power consumption versus FCW input (fixed FCW)       | 128 |

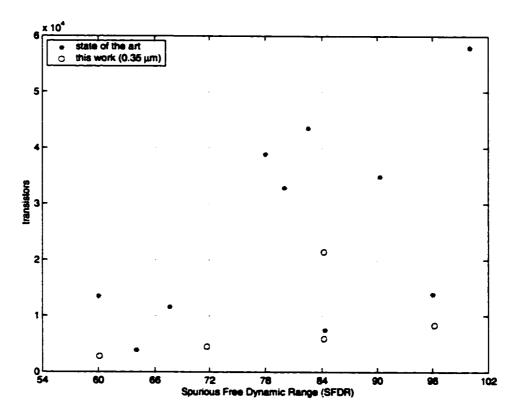

| Figure 7-1 - Complexity and performance summary                        | 132 |

| Figure 7-2 - Comparison of PSAC complexity estimates                   | 134 |

# **List of Tables**

| Table 2-1 - Output noise sequences, M = 3                                     | 18  |

|-------------------------------------------------------------------------------|-----|

| Table 3-1 - Compression factor for number of sub-tables and ROM address width | 29  |

| Table 3-2 - Sine function compression comparison - maximum residual error     | 38  |

| Table 4-1 - Comparison of new and existing techniques                         | 58  |

| Table 6-1 - Candidate slopes sets                                             | 98  |

| Table 6-2 - Selection of a slope set, 8 segments case                         | 99  |

| Table 6-3 - Selected sets of parameters and coefficients                      | 103 |

| Table 6-4 - Synthesis results, 0.18 µm CMOS worst case library                | 116 |

| Table 6-5 - Synthesis results, 0.35 μm typical case library                   | 119 |

| Table 6-6 - Static core power consumption                                     | 123 |

| Table 6-7 - Timing characteristics, chips 1 and 2                             | 124 |

| Table 6-8 - Net core power consumption, random FCW                            | 125 |

| Table 6-9 - I/O power consumption, random FCW                                 | 128 |

| Table 6-10 - Power characteristics, two-FCW frequency hopping                 | 129 |

| Table 7-1 - Complexity and performance comparisons                            | 131 |

# **Acronyms**

ASIC Application Specific Integrated Circuit

CLB Configurable Logic Block

CMC Canadian Microelectronics Corporation

CMOS Complementary Metal Oxide Semiconductor

CORDIC Coordinate Rotation Digital Computer

CRC Communications Research Center

CSD Canonical Signed Digit

DAC Digital to Analog Converter

DC Direct Current

DDF Direct Digital Frequency

DDFS Direct Digital Frequency Synthesizer or Direct Digital Frequency Synthesis

DIP Dual In-line Package

DRDC Defense Research and Development Canada

FCW Frequency Control Word

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

GaAs Gallium Arsenide

HDL Hardware Description Language

HMCS Her Majesty's Canadian Ship

IEEE Institute of Electrical and Electronics Engineers

IO Input / Output

IP Intellectual Property

LFSR Linear Feedback Shift Register

LPF Low Pass Filter

LSB Least Significant Bit

MAE Maximum Amplitude Error

MCL Module Compiler™ Language

MESFET Metal Semiconductor Field Effect Transistor

MSB Most Significant Bit

NA Not Applicable or Not Available

NCO Numerically Controlled Oscillator

PSAC Phase to Sinusoid Amplitude Converter

QDDFS Quadrature DDFS

RMC Royal Military College

ROM Read Only Memory

SFDR Spurious Free Dynamic Range

SiGe Silicon Germanium

SOI Silicon On Insulator

TTL Transistor-Transistor Logic

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

# **Chapter 1**

# Introduction

#### 1.1 Overview

This thesis concerns Direct Digital Frequency Synthesis<sup>1</sup> and Direct Digital Frequency Synthesizers (DDFS<sup>2</sup>). This type of synthesizer offers unique performance characteristics and advantages over designs based on Phase-Locked Loop (PLL) techniques. These include output bandwidths measured in hundreds of megahertz, frequency resolution in the sub-Hertz range, a tuning latency limited to one or a few clock cycles, the ability to maintain phase continuity when tuning, and excellent stability.

Frequency synthesizers generate a waveform of a desired shape at a specific output frequency. The waveform is most often a sinusoid, but it can also be a square wave or a sawtooth. There is normally one input signal of a fixed frequency, known as the reference frequency or standard frequency. The output frequency is usually a rational multiple of the reference frequency, i.e.  $f_{\text{out}} = (p/q) \times f_0$ , where p and q are positive integers, and  $f_{\text{out}}$  and  $f_0$  are the output and reference

<sup>&</sup>lt;sup>1</sup> In the literature, the terms "Direct Digital Frequency Synthesis", "Direct Digital Synthesis", "Numerically Controlled Oscillator" and "Table Look-up Frequency Synthesis" are used by different authors to mean the same thing. The first term, which appears to be the most popular, will be used in this text.

<sup>&</sup>lt;sup>2</sup> The single acronym "DDFS" will be used to mean either Direct Digital Frequency Synthesis or Direct Digital Frequency Synthesizer when the context fully specifies which term is meant. Otherwise, "DDF Synthesis" or "DDF Synthesizer" will be used as appropriate.

frequencies, respectively. In indirect frequency synthesis, the output signal is produced from a secondary oscillator that is locked in phase to the primary frequency reference. In direct frequency synthesis, the output signal is obtained from the standard frequency by a combination of operations such as mixing, filtering, multiplication and division. The output signal's frequency is a function of the reference frequency, without the use of internal oscillators or feedback loops. Direct Digital Frequency Synthesis is a special case of direct frequency synthesis, with digital components alone being used.

The first DDFS architecture was introduced by Tierney, Rader and Gold in 1971 [92]. Realized with 85 discrete TTL packages, it was clocked at just under 820 kilohertz and consumed 12 watts of power. The frequency resolution was 12.5 hertz for an output bandwidth of approximately 400 kilohertz. The severe technology limitations of the time prevented the architecture from gaining wide popularity, and few papers on the subject were published during the following decade [29][93]. The high power consumption, low clock rates and high spectral spurs were seen as major drawbacks of the approach.

A few important DDFS papers were published in the early eighties. Weathley and Phillips [102] observed that the high spurious noise in DDFS output was produced by the periodic nature of the device. They proposed a noise reduction technique that appeared counter intuitive: it was based on the addition of a random noise pattern inside the architecture. Merghardt [62] then provided a first analysis of the output spectra for DDFS. A major breakthrough occurred in 1984 with the publication, by Sunderland et al. [87], of a paper reporting on a first monolithic DDFS realized in 3.5 µm CMOS/SOS technology. The chip was to be used in a spread-spectrum frequency hopping satellite communications system. Capable of generating sinusoids from DC to about 3 megahertz in steps of 7.15 hertz, the synthesizer dissipated only 300 milliwatts.

In 1987, Nicholas and Samueli [66] made an important contribution to the understanding of the spurious levels in DDFS output. Joined by Kim in 1988 [67], the same authors then introduced an optimized DDFS architecture that was to endure as the reference against which all other designs were compared for several years.

Many DDFS patents were issued during this time, showing a growing interest for the technology [103][28][22][77][32][37][101]. These have mainly dealt with noise reduction and with architectures leading to reduced system complexity.

Between 1989 and this day, more than 100 conference and journal papers on DDFS have been published. Dozens of patents have been issued. A monograph by Goldberg [26] has also been published, and Kroupa [44] edited a collection of important DDFS papers in 1999. Novel DDFS designs that advance the limits of clock frequency, output spectral purity and power consumption are a regular feature at the IEEE International Symposium on Solid State Circuits, and in the IEEE Journal of Solid State Circuits.

Direct Digital Frequency Synthesizers have been used in a wide range of applications, including spread spectrum frequency hopping communications [87][11][78][79], and electronic warfare and radar systems [81][2][104][1][89]. Their versatility has also made them ideal candidates in such diverse areas as test instrumentation [19][12][9], broadcasting [96][99], hydrogen maser receivers [61], particle accelerators [35], and medical engineering [24].

### 1.2 Motivation

The phenomenal growth in interest for DDFS has been largely driven by the corresponding growth in wireless communications in the last 20 years, since the synthesis of a sinusoid of a desired frequency is a fundamental requirement in most communication systems. This requirement includes up- and down-conversion through frequency mixing, modulation and demodulation. In frequency-hopping spread-spectrum wireless communication systems, a frequency synthesizer with excellent performance must be used. Requirements include short tuning latency with high precision, excellent output spectral purity, low power consumption and low complexity. The shift to all-digital systems has also favored DDFS research.

There has been extensive research collaboration between the Royal Military College of Canada (RMC), Defense Research and Development Canada (DRDC) in Ottawa and the Communications Research Center (CRC) into the design of digital down converters for radio and electronic

warfare receivers. This has included work on filtering and decimation [13], complex multipliers [54], and quadrature demodulation [108][46]. The last major down-converter building block that had not yet been addressed was the local oscillator. It was therefore proposed by CRC to study DDFS architectures, with the initial aim of integrating such a device together into existing down converter research. This proposal was the seed that led to the research presented in this thesis.

## 1.3 Research Objectives

The following goals and objectives were established for this research:

- to discover innovative sinusoid generation techniques for use in DDFS in order to reduce system complexity, when compared with prior work, while maintaining superior output spectral characteristics and high data rates;

- to apply these techniques to the development of novel DDFS architectures suitable for fast frequency hopping, low power wireless communications systems;

- to define metrics to evaluate DDFS system performance and costs early in the design cycle;

- to simulate, implement, and test several DDFS designs in order to compare the proposed techniques and architectures with prior work; and,

- to develop a behavioral synthesis capability for a DDFS Intellectual Property (IP) block for inclusion into a general-purpose or tailored communication system.

# 1.4 Synopsis

This thesis is divided into 8 chapters including this introduction. Chapter 2 presents an overview of the traditional DDFS architecture, and it discusses its main operating and performance parameters. Chapter 3 presents the state of the art in Phase to Sinusoid Amplitude Converter (PSAC) architectures for use in DDFS. Chapter 4 presents a new method and architecture for ROM data amplitude compression. Chapter 5 presents a generalized architecture based on linear interpolation, analyzes its output spectrum, and provides a systematic design approach. Chapter 6 presents new hardware-optimized DDFS architectures exploiting the analysis and design

procedure described in Chapter 5. Several design examples are given, together with implementation data in FPGA, 0.35  $\mu m$  CMOS and 0.18  $\mu m$  CMOS. Chapter 7 contains an interpretation and discussion of the results and a comparison with existing work. Conclusions are found in Chapter 8.

# **Chapter 2**

# Principles of Direct Digital Frequency Synthesis

# 2.1 Direct Digital Frequency Synthesizer Architecture

## 2.1.1 General Description

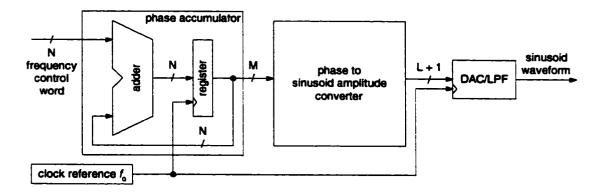

Most Direct Digital Frequency Synthesizers are derived from the architecture introduced by Tierney, Rader and Gold [92] in 1971. This architecture can be divided into three blocks: a phase accumulator, a Phase-to-Sinusoid Amplitude Converter (PSAC), and a Digital-to-Analog Converter (DAC) with a Low Pass Filter (LPF). The system has two inputs: a reference clock of frequency  $f_0$  and a frequency control word (FCW). A single phase version of the architecture is shown in Figure 2-1.

The phase accumulator is made up of an adder and a register, both N bits wide. On every clock cycle, the phase accumulator integrates the value of the FCW, hence the value stored in the register increases with time, eventually overflows past zero, and the cycle starts again. The phase accumulator output is therefore a ramp whose slope is directly proportional to the FCW. After n clock cycles, the value stored in the phase accumulator register is equal to

$$\langle n \times FCW + p_0 \rangle_{2^N}$$

$n = 0,1,2,3,...$  (2-1)

where  $\langle \ \rangle_{2^N}$  denotes the modulo- $2^N$  operation, and  $p_0$  is the phase accumulator's initial contents upon reset. This value is generally 0.

Figure 2-1 - Single-phase sinusoid output DDFS architecture

The phase accumulator's contents can be interpreted as a portion of a rotation around a unit circle. The equivalent phase angle is equal to

$$\varphi(n) = \frac{2\pi}{2^N} \langle n \times FCW + p_0 \rangle_{2^N} \quad n = 0, 1, 2, 3, ...$$

(2-2)

The role of the PSAC is to calculate an approximation of the sine of this angle. The approximation is quantized with L + 1 bits, which can be viewed as L bits of amplitude and one of sign. Ideally, the PSAC output is equal to

$$A \times \sin \varphi(n)$$

(2-3)

where A is some amplitude that can be selected to maximize the synthesizer's output dynamic range. If the PSAC output is interpreted as a fraction, then the greatest value of A is  $(2^L - 1) / 2^L$ . In practice, the output of the PSAC includes a noise amplitude not indicated in Equation (2-3). This will be discussed in more detail below.

In its simplest form, the PSAC is implemented as a ROM Look-Up Table (LUT). The number of ROM words and the word width determine the angular and amplitude resolutions of the synthesizer, respectively. These in turn affect the synthesizer's output noise characteristics.

The role of the DAC and LPF is to convert the sequence of digital sinusoid samples into an analog waveform. These components are not present if the digital sequence is used directly in a digital system.

## 2.1.2 Tuned Frequency and Effect of the Frequency Control Word

As shown in Equation (2-2), the effective angle increment on every clock cycle is directly proportional to the ratio of the FCW to the number of states of the phase accumulator:

$$\Delta \varphi = \varphi(n) - \varphi(n-1) = 2\pi \times \frac{FCW}{2^N}$$

$n = 1, 2, 3, ...$  (2-4)

The angular frequency of the ramp output from the phase accumulator, which is also the synthesizer's output angular frequency, is therefore given by:

$$\omega_{out} = \frac{\Delta \varphi}{T_0} = f_0 \times \Delta \varphi = 2\pi f_0 \times \frac{FCW}{2^N}$$

(2-5)

in radians/second, where  $T_0$  and  $f_0$  are the period in seconds and the frequency in hertz of the clock reference, respectively. The synthesizer's output frequency is equal to:

$$f_{out} = \frac{\omega_{out}}{2\pi} = f_0 \times \frac{FCW}{2^N}$$

(2-6)

in hertz.

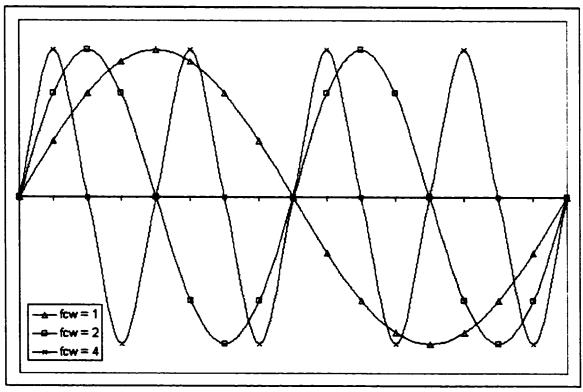

For small FCW (and hence small phase increment), more samples will be obtained from the PSAC per unit time, leading to a low frequency. For large FCW, the sine amplitudes will be scanned more quickly producing a higher frequency. This is shown in Figure 2-2, where it is assumed that the PSAC is implemented with a ROM LUT storing 16 samples of the sine function. Three curves are shown, corresponding to three values for the FCW. For the value 1, all samples are retrieved in order and the output frequency is the lowest possible above DC. For the value 2, every other sample is skipped. For the value 4, three samples are skipped per clock cycle.

#### 2.1.3 Frequency Resolution

Equation (2-6) can be re-written as:

$$f_{out} = FCW \times \frac{f_0}{2^N} \tag{2-7}$$

The ratio of the clock reference to the number of states of the phase accumulator represents the frequency resolution of the synthesizer:

$$\Delta f = \frac{f_0}{2^N} \tag{2-8}$$

This equation implies that the frequency resolution of the synthesizer can be made arbitrarily small by choosing as large an N as necessary. In practice, the width of the phase accumulator would be limited by system size and performance considerations. However, with a clock reference of 100 MHz and a typical phase accumulator width of 32 bits, the frequency resolution of the synthesizer is less than 0.025 Hz, which is adequate in most applications. Every additional bit in the phase accumulator improves the frequency resolution by a factor of two.

Figure 2-2 - Varying the output frequency by skipping samples

### 2.1.4 Tuning Bandwidth

When the FCW is equal to 0, the synthesizer's output is a constant equal to the sine amplitude of the present phase angle. The lowest non-zero frequency occurs when the FCW is set to one, and it is equal to the frequency resolution of the synthesizer:

$$f_{\min} = 1 \times \Delta f = \frac{f_0}{2^N} \tag{2-9}$$

The maximum theoretical frequency is dictated by the Nyquist criterion. Its upper bound is equal to half of the reference frequency:

$$f_{\text{max}} < \frac{f_0}{2} = 2^{N-1} \times \Delta f \tag{2-10}$$

The value of the FCW must effectively be less than  $2^{N-1}$ , and its width is limited to N-1 bits. For quadrature output synthesizers (discussed below), however, the FCW may be expressed as an N-bit signed integer since output signals with negative frequencies are then possible.

In practice, for analog output DDF Synthesizers, the maximum frequency is limited to approximately  $3f_0/8$  to simplify the design of the low-pass filters that follow the DACs. The tuning bandwidth therefore extends from DC to less than half of the reference frequency, as limited by practical filter design considerations.

## 2.1.5 Tuning Latency

The maximum rate at which the FCW can be changed and the time it takes for the output signal to stabilize on the new frequency are of prime importance in frequency-hopping spread-spectrum communications systems.

In a DDF Synthesizer, the tuning latency can be limited to a single clock cycle, which is extremely fast. The critical path is often placed in the phase accumulator, especially if it is very wide to accommodate fine frequency resolution (Equation (2-8)). Alternatively, the critical path may be in the PSAC. This can be the case for ROM architectures if the ROM is very large, and also for ROM-less architectures if the calculations inside the PSAC are complex.

In order to increase the synthesizer's tuning bandwidth, it is necessary to increase the reference clock's frequency. This may require pipeline registers to be included in the critical path. In such a case, the tuning latency of the synthesizer is increased by one clock cycle for every stage of pipelining added inside the synthesizer. Still, assuming that 10 levels of pipelining are used, the tuning latency is limited to 20 nanoseconds for a 500 megahertz clock.

## 2.1.6 Phase Continuity upon Tuning

DDF Synthesizers have the unique characteristic that phase continuity is maintained when changing the output frequency. This is a consequence of using a phase accumulator: when the FCW is changed, its new value is simply added to the existing sum in the phase accumulator. Thus, the present phase information is kept and the sinusoid at the new frequency starts from this same phase.

## 2.1.7 Frequency and Phase Modulation

An interesting aspect of DDF Synthesizers is that frequency and phase modulation can be easily imposed on the sinusoid output signal.

Since the FCW determines the instantaneous frequency of the output signal, frequency modulation is accomplished by simply varying the value of the FCW. For example, a "chirp" waveform can be easily synthesized by using a counter to generate a ramp as the FCW. The slope of this ramp determines the rate of frequency change within the chirp. Its bounds determine the chirp's lower and upper frequencies.

Phase modulation is accomplished by adding a modulating signal to the phase word prior to accessing the PSAC. For example, Quadrature Phase Shift Keying can be realized by adding one of four constant values to the phase word. The constant to be added is selected based on a control signal representing the data to be encoded.

## 2.1.8 Other Output Types

The architecture presented in Figure 2-1 can be modified so that the system output is not a sinusoid.

A popular form of DDF Synthesizer, often referred to in the literature as Numerically Controlled Oscillator (NCO), has a square wave (or clock) output. It can be realized simply by eliminating the PSAC, the DAC and LPF, and using the phase accumulator's MSB as the output signal.

A ramp can also be generated by passing a desired number of most significant bits from the phase accumulator directly to the DAC and LPF. Alternatively, a triangular wave can be generated by increasing and decreasing the phase accumulator contents on alternate half-periods. This can be realized by applying a one's complement operation to the phase accumulator output when the MSB is a '1'. The technique is further described in the following section, as it can also applied to sinusoid output synthesizers.

Finally, the PSAC can be replaced by a table storing samples from any periodic function. The synthesizer will then be able to reproduce this function with a varying frequency.

Unless explicitly specified, this dissertation only considers sinusoid output DDFS.

# 2.2 Phase to Sinusoid Amplitude Converter Complexity Reduction

The complexity of the PSAC has a significant impact on a DDF Synthesizer's performance and cost. This block has therefore been the subject of intense research. In this section, basic PSAC complexity reduction techniques are discussed. More advanced techniques will be described in Chapter 3.

### 2.2.1 Phase Angle Truncation

From the block diagram of Figure 2-1, three separate bus widths define the traditional DDF Synthesizer:

- N, the width of the adder, register and FCW;

- M, the width of the addressing lines to the PSAC; and

- L+1 (for L bits of magnitude and one of sign), the width of the PSAC data.

From Equation (2-8), it is seen that increasing N improves the synthesizer's frequency resolution. In practice, it is advantageous to have a large N for fine frequency resolution. However, if the PSAC is implemented with a ROM Look-Up Table, using all N bits to address the ROM would lead to a very large memory. Accordingly, the phase value is normally truncated to retain only M

most significant bits. Memory requirements are reduced accordingly without sacrificing frequency resolution. However, this truncation causes a periodic amplitude error in the synthesized waveform which causes spurious noise in the output spectrum. This is discussed in greater detail in Section 2.3.2.

If the PSAC is implemented as a ROM Look-Up Table, total storage requirement are therefore equal to:

ROM size (bits) =

$$(L+1)\times 2^M$$

(2-11)

This equation shows that the ROM size grows exponentially with the width of the truncated phase angle, and linearly with the amplitude resolution of the output data.

## 2.2.2 Exploiting Quadrant Symmetry

A very simple ROM size reduction technique for a DDF Synthesizer is based on exploiting the quarter-wave symmetry property of the sine function. The approach was first described by Tierney et al. [92], and was used by virtually every researcher thereafter. Notable exceptions are Saul and Mudd [80] and Saul and Taylor [81], for unexplained reasons, and Sodagar and Lahiji [83][85], for algorithmic reasons. The exploitation of quarter-wave symmetry normally has no effect on the selection of other ROM size reduction strategies, and should almost always be used.

As a first step, all angles must be mapped to the interval  $[0, 2\pi]$ . In DDFS, this is accomplished trivially by the modulo- $2^N$  operation of the phase accumulator. The second step consists of mapping angles that lie in the third and fourth quadrants to angles in the second and first quadrants in order to calculate their sine amplitudes:

$$\sin(\theta) = \begin{cases} \sin(\theta) & 0 \le \theta < \pi \\ -\sin(\theta - \pi) & \pi \le \theta < 2\pi \end{cases}$$

(2-12)

The final step consists of mapping resulting angles that lie in the second quadrant to angles in the first quadrant:

$$\sin(\theta) = \begin{cases} \sin(\theta) & 0 \le \theta < \frac{\pi}{2} \\ \sin(\pi - \theta) & \frac{\pi}{2} \le \theta < \pi \end{cases}$$

(2-13)

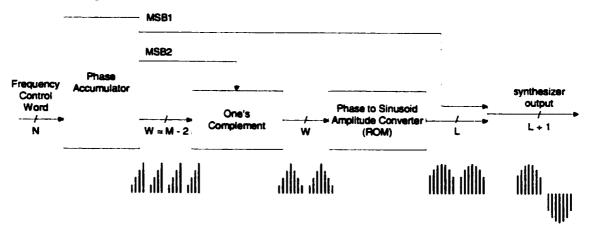

A very elegant way of implementing this process of reconstructing a full sinusoid from first quadrant samples alone was proposed by Tierney et al. [92]. It was illustrated concisely and clearly by Manassewitsch [60], Figure 1-20, and an adapted diagram is given in Figure 2-3. The method is based on the observation that the two MSBs of the phase word identify which quadrant an angle belongs to.

Figure 2-3 - Quarter-wave symmetry (from [60])

The phase angle MSB indicates whether an angles lies in the first two quadrants (a '0') or in the latter two quadrants (a '1'). Hence, the MSB readily provides the sign of the sine amplitude. Considering only the remaining portion of the phase angle word effectively maps an angle to the first and second quadrants (the operation  $\theta - \pi$  in Equation (2-12)).

Inspecting the second MSB identifies whether the resulting angle is in the second (a '1') or first (a '0') quadrant. The operation  $\pi - \theta$  in Equation (2-13) is implemented by 'counting down' from the phase angle  $\pi/2$  instead of 'counting up' from 0. Hence, the second MSB controls a one's complementor that inverts the remaining phase angle bits as necessary.

The memory storage requirements are significantly reduced from what was specified by Equation (2-11). First, the number of necessary ROM words is divided by four. Further, the ROM word width is reduced by one bit, since only positive values must be generated and the sign information is provided directly by the phase angle MSB. For a LUT implementation, storage requirements are then:

ROM size (bits) =

$$L \times 2^{M-2}$$

(2-14)

The so-called memory compression ratio is therefore equal to:

$$\frac{(L+1)\times 2^{M}}{L\times 2^{M-2}} = \frac{4\times (L+1)}{L}$$

(2-15)

There is a consequence to scanning first quadrant angles up or down with the help of the one's complementor. When calculating the data that must be stored into or calculated by the PSAC, a phase shift equal to  $\pi/2^M$  must be introduced. This peculiarity was observed by Nicholas et al. [67] and described further by Vankka [97]. The reasoning is explained here.

Assume that the phase accumulator reset value is 0 and the FCW is 1. Also assume that the PSAC is implemented with a ROM. The first accessed ROM address is 0, and the last ROM address accessed in the first quadrant is  $2^{M-2} - 1$ . On the following clock cycle, the second MSB of the phase accumulator changes from 0 to 1 and all other bits are zero. The 1's complement block is activated and the M-2 least significant phase accumulator bits are inverted, from zeros to ones. The accessed ROM address is therefore  $2^{M-2} - 1$  twice in a row. A similar situation occurs when the contents of the phase accumulator change from the last angle of the second quadrant to the first angle of the third quadrant, but this time it is memory address 0 that is accessed twice in a row.

The data stored in address 0 should therefore be offset from sin(0) by an angle equal to half of the angular resolution  $\Delta \varphi$ , which is the angle difference between the sinusoid samples of successive memory cells shown in Equation (2-4). Instead of the ROM storing the values of sin(0),  $sin(\Delta \varphi)$ ,  $sin(2 \times \Delta \varphi)$ , ...., and  $sin(\pi/2 - \Delta \varphi)$ , it should store the values of  $sin(\Delta \varphi / 2)$ ,  $sin(3 \times \Delta \varphi / 2)$ ,  $sin(5 \times \Delta \varphi / 2)$ , ...., and  $sin(\pi/2 - \Delta \varphi / 2)$ .

#### 2.2.3 Quadrature Sinusoid Outputs Architecture

The DDFS synthesizer introduced by Tierney et al. [92] had quadrature outputs. The authors noted that this allowed the bandwidth of the synthesizer to be doubled, as compared with a single phase case, for a given reference frequency. This is because the generation of quadrature outputs implies that it is possible to specify a negative frequency. Therefore, the FCW can be interpreted as an N-bit two's complement number. If the synthesizer's quadrature output is up-converted by some mixing process, then its bandwidth is effectively doubled from the single phase case, at no increase in reference clock frequency. However, Tierney et al.'s architecture required two accesses of the PSAC per clock cycle in order to compute the quadrature outputs. An alternative would have been to double memory and processing requirements.

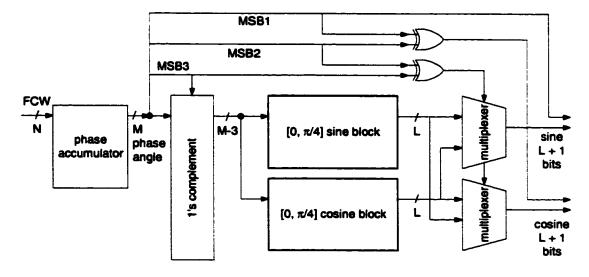

The eighth-wave symmetry of the sine and cosine functions can be exploited instead, and two PSAC blocks are used. The blocks generate the sine and cosine for angles in the interval  $[0, \pi/4]$  only, and hence the complexity of each block is half of the complexity of the PSAC for the single-phase case. The overall computational complexity for calculating sinusoid amplitudes is therefore unchanged. This architecture was first proposed by Tan and Samueli [90], and it is shown in Figure 2-4.

Figure 2-4 - Quadrature DDFS Architecture (from [90])

The three MSBs of the phase angle identify one of eight octants around the unit circle. The first MSB again provides the sign of the sine function, and, when XOR'ed with the second MSB, the result gives the sign of the cosine function. A second XOR gate accepts as inputs the second and third MSBs of the phase angle. Its output is a control signal for two 2:1 multiplexers which select a PSAC block output to reconstruct the sine and cosine waves. The third MSB controls the 1's complement block that implements the count-up or count-down process of the phase angle.

## 2.3 Output Noise

The noise performance of a DDF Synthesizer is normally specified by the Spurious Free Dynamic Range (SFDR), also known in the literature as Spectral Purity. The SFDR is defined as the ratio of the power in the desired frequency to the power in the greatest undesired frequency spur. It is normally expressed in decibels with respect to the carrier (dBc).

Several researchers provided descriptions of the noise spectra of DDF Synthesizers, including Tierney et al. [92], Mehrgardt [62], Kisenwether and Troxell [38], Nicholas and Samueli [66], Mattison & Coyle [61], Garvey and Babitch [23], Kroupa [40][41][42][43][45], and Torosyan and Willson [94].

In this section, we will consider the SFDR of the digital output sequence of the synthesizer. We are not considering analog noise introduced by the DAC or the LPF.

#### 2.3.1 Noise Due to Amplitude Error

We will assume that the PSAC output sequence is invariant with time, i.e. the output amplitude is always the same for a given angle. Given the digital nature of DDFS, this is the default case. Without loss of generality, and to simplify the analysis, we will assume that quadrant symmetry is not used. The PSAC is therefore able to provide a sine amplitude estimate for  $2^M$  distinct angles. Let  $m \in \{0, 1, 2, ..., 2^M - 1\}$  be the M-bit phase angle that is passed to the PSAC. The PSAC output sequence, which we denote by f(m), is equal to:

$$f(m) = A\sin(\frac{2\pi m}{2^M}) + \varepsilon(m)$$

$m = 0,1,2,3,...,2^M - 1$  (2-16)

where  $\varepsilon(m)$  is the error sequence between the PSAC output and an ideal sine wave sequence of amplitude A expressed with infinite precision. The error sequence results from several factors, including the amplitude quantization error. Assuming that some processing is performed by the PSAC instead of using a ROM, any algorithmic error made in the calculation of f(m) also affects the error sequence. The output frequency spectrum of the synthesizer therefore has two components: a pure sine wave of amplitude A, which is the desired system output, and some noise due to the amplitude error on the output samples. The noise spectrum can be calculated precisely by taking the Discrete Fourier Transform of one period of the noise sequence.

Let us assume that N = M, i.e. that no phase truncation is done. The case for N > M is considered in the next section. The value of the FCW affects the order with which the noise sequence  $\varepsilon(m)$  comes out of the synthesizer. For even values of FCW, not all noise sequence samples appear at the output. However, for odd values of the FCW, the repetition period of the noise samples will always be M, i.e. it will take exactly M changes in the phase accumulator before the sequence starts to repeat.

For example, assume that M=3. There are four possible sequences for non-zero FCW values consistent with the Nyquist rate (i.e. FCW  $\in \{1, 2, 3\}$ ). They are listed in Table 2-1.

| FCW | fequence                                                                                                                                                                                                         | noise period |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1   | ε(0), ε(1), ε(2), ε(3), ε(4), ε(5), ε(6), ε(7), ε(0), ε(1), ε(2),                                                                                                                                                | 8            |

| 2   | $\epsilon(0), \epsilon(2), \epsilon(4), \epsilon(6), \epsilon(0), \epsilon(2), \epsilon(4),$                                                                                                                     | 4            |

| 2   | $\epsilon(1), \epsilon(3), \epsilon(5), \epsilon(7), \epsilon(1), \epsilon(3), \epsilon(5),$                                                                                                                     | 4            |

| 3   | $\varepsilon(0)$ , $\varepsilon(3)$ , $\varepsilon(6)$ , $\varepsilon(1)$ , $\varepsilon(4)$ , $\varepsilon(7)$ , $\varepsilon(2)$ , $\varepsilon(5)$ , $\varepsilon(0)$ , $\varepsilon(3)$ , $\varepsilon(6)$ , | 8            |

Table 2-1 - Output noise sequences, M = 3

We observe that for a value of FCW equal to 2, the noise sequence depends on whether the initial value of the phase accumulator is an even or odd number. In either case, only half of the noise samples corresponding to a FCW equal to one contribute to the output noise sequence. Consequently, the output spectrum is expected to vary with the initial phase accumulator value. We also observe that for values of FCW equal to 1 or 3, the noise sequence includes all noise samples but in a different order.

This observation has a fundamentally important consequence for the analysis and design of DDF Synthesizers. A change in FCW results in a change in the order of the noise samples out of the synthesizer and in a corresponding change in the position of discrete frequency components in the noise spectrum. However, the amplitudes and number of the noise frequency components do not change. Consequently, studying the noise spectrum corresponding to one value of FCW allows the exact prediction of the noise spectrum corresponding to all other values of FCW that produce noise sequences based on the same set of samples. The reader is referred to the papers by Nicholas and Samueli [66] and Vankka [97] for a full description of this principle and for a proof.

Consequently, in most cases it is advantageous to restrict the value of the FCW to odd numbers only. This way, the output spectrum of the synthesizer can be determined by generating a single output noise sequence and calculating its spectrum. It is therefore simple, during the design process, to evaluate and compare different architectures or architecture parameters. There is also a second advantage in the presence of phase truncation spurs, discussed in the following section.

Forcing an odd value of FCW is fairly simple, by hard-wiring a '1' as the LSB of the FCW. Instead of reducing the frequency resolution by a factor of 2, the phase accumulator can be made one bit wider to accommodate the hard-wired '1'. The effect on system complexity and timing is normally insignificant, especially for large N (i.e. greater than 20). A small frequency offset is introduced, however. The synthesizer's output frequency becomes:

$$f_{out} = \frac{\omega_{out}}{2\pi} = f_0 \times \frac{2FCW + 1}{2^{N+1}} = f_0 \times \frac{FCW + \frac{1}{2}}{2^N}$$

(2-17)

in hertz.

Nicholas and Samueli [66] proposed an elegant technique to force an odd FCW. It consists of generating the sequence {0, 1, 0, 1, 0, ...} with the help of feedback loop composed of an inverter and a D-register, and feeding this sequence to the input carry port of the phase accumulator.

#### 2.3.2 Noise Due to Phase Truncation

As discussed previously and shown in Equation (2-8), a large phase accumulator width is normally required to achieve fine frequency resolution. However, the complexity of the PSAC varies exponentially with the width of the phase word. Hence, as discussed in Section 2.2.1, the phase word is normally truncated from N to M bits, N > M. Thus, the frequency resolution of the synthesizer is unaffected. However, spurious noise is introduced in the synthesizer output.

This phenomenon has been well described by Nicholas and Samueli [66], Kroupa et al. [45], and, more recently, by Torosyan and Willson [94]. It has been shown that the worst case spurs are  $6 \times M$  decibels down from the fundamental, provided that N > M + 4, i.e. that at least 5 bits are truncated.

#### 2.3.3 Phase Noise

Phase noise is not often considered or reported for sine-output DDFS, for a number of reasons.

It is normally assumed that a DDFS behaves as a digital frequency divider, for which the output phase noise is equal to the input reference's phase noise, divided by the square of the relative output signal frequency (see the introductory paper for part VII, in [44]):

$$S_{\varphi,out} = S_{\varphi,in} \times \left(\frac{FCW}{2^N}\right)^2 \tag{2-18}$$

where  $S_{q,ost}$  and  $S_{q,in}$  are the output signal and reference frequency phase power spectral densities, respectively. In general, the phase noise of the reference frequency is low enough that the system performance is limited by the frequency spurs due to sample amplitude error and phase truncation. For an analog output DDFS, the limited slew-rate of the DAC is an important contributor to phase noise [61].

#### 2.3.4 Noise Reduction Techniques

As discussed above, the digital nature of DDF Synthesizers implies that the error amplitude for any angle is invariant with time. For a fixed value of FCW, the same error samples are generated with a period that depends on the FCW, and the resulting sequence's frequency spectrum is generally not white. Again, if the FCW is restricted to an odd number, the noise sequence period is equal to the number of states of the phase accumulator.

In order to reduce the amplitude of the greatest spurs in the output frequency spectrum, the periodicity of the noise must be eliminated. There are two main methods of accomplishing this, and they consist of adding a pseudo-random sequence to the phase word before it is applied to the PSAC, or to the amplitude obtained from the PSAC. The pseudo-random sequence can be generated by a Linear Feedback Shift Register (LFSR) with a very long period. The effective error sequence period is therefore made very long, which results in a significant reduction in the amplitude of distinct frequency spurs. A drawback of the method, however, is that the overall noise floor is raised.

Several researchers have proposed variations and combinations of these two approaches. Wheatley et. al. [102] and Wheatley [103] were the first to propose this randomization process. Their work was directed to a clock-output DDFS instead of the sinusoid output type that has been discussed so far. In a clock-output (or square wave output DDFS), the most significant bit of the accumulator is used as a clock signal. In Wheatley's system, the pseudo-random sequence is added to the content of the phase accumulator. Jasper [32] applied Wheatley's technique to the sine output DDFS, with the consequence that the PSAC complexity, in terms of number of words and of word width, was reduced while maintaining the same level of SFDR. Kerr and Weaver [37], then Reinhardt et. al. [77], applied a random sequence to the output data from the PSAC, prior to driving the DAC. Finally, Flanagan and Zimmerman [21] combined the two approaches. These authors provided a detailed analysis of adding dithers to both the phase word and the sine amplitudes, and proposed a design achieving very good performance. The drawback, however, is

the added system complexity due to the inclusion of two LFSRs (18 and 16 bits wide) and two 16-bit wide adders in the data path.

A mention should also be made of the work by O'Leary and Maloberti [72], who proposed a more simple approach. It consists of inserting a noise shaper, built by grouping an adder and a register, between the output of the phase accumulator and of the ROM. The adder's first input is the phase accumulator. The adder's high order output bits address the ROM, and the low order bits are registered and fed back to the adder's second input.

Vankka [98] presented a concise review of spur reduction techniques for DDFS. He then introduced three new methods that are variations of the work presented above. The first method involves the option of switching the extra '1' as the LSB of the phase accumulator on or off, depending on the value of the FCW. This way, for those values of the FCW that do not produce high spurious output, the noise floor is kept low. The second method involves high-pass filtering of the dither sequences prior to their addition to the phase word or to the sinusoid amplitude. The advantage of this approach is that while the noise floor is increased, as discussed above, most of the noise power is high in the frequency band. Consequently, a large portion of it lies in the stop band of the synthesizer's analog LPF, and is hence removed. The third method introduces filtering directly in the phase angle datapath or in the sine amplitude datapath.

## 2.4 Clock Output DDFS

In the literature, several papers claim to implement so called ROM-less DDF Synthesizers with very low complexity and high SFDR. However, when discussing ROM-less approaches, it is important to distinguish between sine-output and square-wave-output DDF Synthesizers. The latter are normally much simpler than the former.

The confusion in terminology can be traced back to some early DDFS papers [7][76]. When implementing a clock output DDFS, phase jitter tends to be a problem because, for most values of the FCW, the accumulator does not cycle to the zero value on every period. An early solution to this problem was to generate a sine wave with the help of a ROM LUT and a DAC/LPF block

(i.e. the architecture discussed so far and shown in Figure 2-1), then to use a limiting circuit to produce a square wave. This was obviously a fairly expensive and complex way of generating a jitter-reduced clock, but it worked well since the phase noise performance predicted by Equation (2-18) could be attained provided that the DAC linearity was sufficiently high.

Several researchers have since published papers claiming high SFDR for ROM less approaches, but their architectures generate clock signals. Hence, the SFDR is only measured from DC to the third harmonic of the clock. Phase noise then becomes a much more important performance parameter than SFDR.

This dissertation is concerned only with sinusoid output DDF Synthesizers. Therefore, the interested reader is referred to several papers on jitter reduction for clock output DDFS: Nakagawa and Nosaka [64], Nosaka, Nakagawa, and Yamagishi [71] Yamagishi, Nosaka, Muraguchi and Tsukahara [107], Nieznanski [70], and Calbaza and Savaria [8].

# 2.5 System Performance Parameters and DDFS Complexity Metrics

In this section, we summarize the system performance parameters and complexity metrics that must be considered when comparing the relative merits of two DDF Synthesizers. The reader is also referred to Reinhardt et al. [76] and Manassewitsch [60] for a broader discussion on the performance of various types of synthesizers.

#### 2.5.1 Performance Parameters

The following parameters define the performance of DDF Synthesizers:

Spurious Free Dynamic Range (SFDR): the power ratio between the greatest undesired frequency spur and the frequency of interest, normally expressed in decibels relative to the frequency of interest or carrier (dBc);

- maximum clock rate: the maximum frequency of reference signal determines the synthesizer's tuning bandwidth, since it extends from DC to less than half of the reference signal's frequency;

- 3. <u>frequency resolution</u>: the frequency resolution is determined by the phase accumulator width and the reference signal's frequency; hence, the relative frequency resolution of two designs with different maximum clock rates can be compared by considering the widths of their phase accumulators only;

- tuning latency: the tuning latency is determined by the number of pipeline stages in the data

path; the latency is equal to p + 1 clock cycles, where p indicates the number of pipeline

stages;

- 5. <u>output type</u>: the output is generally either a sinusoid or a square wave; for sinusoid output DDFS, single phase or quadrature outputs may be available:

- 6. <u>output data format</u>: exploiting quadrant symmetry, as discussed in Section 2.2.2, naturally favors the sign and magnitude format for the output data; however, another format is often required, such as unsigned representation for DACs; in low-SFDR DDFS, this conversion process can require a significant increase in system resources; and,

- modulation and/or demodulation capability: modulation and demodulation capability, if

present, must be well described as it adds a significant amount of complexity to the

synthesizer.

There are other performance parameters that apply to all frequency synthesizers. For DDFS, however, they are secondary due to the nature of the system. For example, stability of a DDFS is normally a function of the reference clock only, although the DAC's performance could vary with time due to aging of its analog components. Other such parameters include the type of required references, the output level, the flatness, stability and accuracy of the output signal amplitude, and the possibility of synchronization with an external reference.

#### 2.5.2 Hardware Implementation Complexity Metrics

When comparing two implemented DDF Synthesizers of equal or comparable performance, several metrics can be used. First, however, the technology must be fully specified in order for the comparison to be meaningful. For ASICs, this includes the nature of the manufacturing process (CMOS, GaAs, SiGe, SOI, etc.), the minimum feature size  $(0.6 \, \mu m, \, 0.35 \, \mu m, \, 0.18 \, \mu m,$  etc.) and the cell library used. For FPGA implementations, it includes the FPGA family and speed grade. In all cases, the operating voltage and temperature must also be specified as they have a significant impact on power consumption and maximum clock rate.

#### The metrics are:

- core area (for ASIC technologies): when reporting the total core area used by the design, it is

essential to specify whether the area includes only the total area occupied by the core cells, or

if it is the total core area after cell placement and routing;

- 2. core power consumption: when reporting core power consumption, the results must be further qualified by specifying whether they have been obtained from simulation or by measurements of an implemented chip; in the case of simulation, it should also be specified whether the simulation includes interconnect parasitics extracted from placement and routing information;

- number of core cells or FPGA blocks: the number of core cells or FPGA blocks used by the

design can be readily obtained after synthesis; and,

- 4. number of equivalent core gates and/or core transistors: this popular design complexity metric can unfortunately be measured several ways; for FPGA implementations, the synthesis tool can report an estimate based on the number of used blocks and the relative utilization of each block's resources; for designs implemented in ASICs, there are four possibilities:

- a. the total area occupied by the core cells can be divided by the area of a reference cell, such as the smallest 2-input NAND gate, to obtain an equivalent gate count, and the equivalent number of transistors is obtained from multiplying this number by the number of transistors in the reference cell;

- b. the list of core cells can be inspected, and the expected number of transistors for each cell can be estimated (2 for an inverter, 4 for a 2-input NAND gate, etc.); however, it must be noted that cell libraries typically include several cells realizing the same Boolean function albeit with different timing and power consumption characteristics;

- c. the total core area can be divided by a design density parameter specified by the cell library vendor, providing an equivalent gate or transistor count; and,

- d. some synthesis and placement tools provide the option of reporting the number of transistors in a design.

## **Chapter 3**

# State of the Art in Phase to Sinusoid Amplitude Conversion

It has already been stated that, in its simplest incarnation, the Phase to Sinusoid Amplitude Converter (PSAC) is realized as a ROM look-up table. However, its size tends to be large for good SFDR performance, increasing power consumption and system area, and decreasing the maximum clock rate. In Section 2.2, we considered two basic techniques to achieve ROM size reduction, to wit: phase accumulator truncation and exploiting the quadrant or octant symmetry of the sine function for single phase and quadrature output DDFS, respectively.

This chapter includes a review of the state of the art in PSAC architectures for DDFS. It also discusses techniques that have been proposed to implement this block with the least possible complexity for a given performance level.

## 3.1 Angular Decomposition

Significant memory savings can be made by segmenting the ROM into "coarse angle" and "fine angle" sub-tables, retrieving values from each on every clock cycle, and adding processing to derive a correct sine function approximation.

#### 3.1.1 Tiemey et al.: Sum of Angles and Multiplication

As a first step, Tierney et al. [92] and Tierney [93] suggested breaking the phase angle into a sum of sub-angles. A complex sample is kept in memory for the value of the complex exponential evaluated at each sub-angle. Since the exponential of a sum of values is the product of the

exponentials of each value, a complex multiplication must be done on the ROM data. For example, if the phase accumulator angle  $\theta$  is expressed as the sum

$$\theta = \sum_{i} \theta_{i} \tag{3-1}$$

then the complex exponential corresponding to this angle can be calculated as

$$e^{j\theta} = e^{j\sum_{i}\theta_{i}} = \prod_{i}e^{j\theta_{i}}$$

(3-2)

For the implementation, the partition of the phase accumulator word into sub-words is very simple. The phase accumulator word can be split into S slices of adjacent bits. As an example, assume that quadrant symmetry is used, the truncated phase word width is M = 14 bits and the ROM address bus is W = 12 bits wide. If W and S are not relatively prime, as in this case, then each slice can contain the same number of bits. Here, the ROM can be decomposed into 3 subtables, with the 4 most significant bits (bits 8 to 11) of the phase word addressing one table, bits 4 to 7 addressing a second table, and the 4 least significant bits (bits 0 to 3) addressing a third table. In this case, the most significant slice represents a "coarse" angle, the middle slice represents an angle with "middle" granularity, and the least significant slice represents a "fine" angle. The two complex multiplications represent "middle" and "fine" rotations from the coarse angle.